新華社最新消息�����,我國率先搭建了國際首個(gè)通信與智能融合的6G外場(chǎng)試驗網(wǎng)�����,實(shí)現了6G主要場(chǎng)景下通信性能的全面提升��?�;?G場(chǎng)景對時(shí)鐘信號的高要求���,賽思設計了一種開(kāi)環(huán)結構的小數分頻鎖相環(huán)量化噪聲校準技術(shù)�����,并自研了高性能SOC時(shí)鐘芯片產(chǎn)品�����。

6G照進(jìn)現實(shí)����,對時(shí)鐘信號有更高要求

相較于5G���,6G不僅能夠達到更高速率����、更低時(shí)延��、更廣的連接密度��,還能實(shí)現通信與人工智能��、智能感知的深度融合��。這也意味著(zhù)“快”只是6G通信技術(shù)中的一個(gè)基礎體現���,協(xié)同感知的智能管理才是其顛覆性的創(chuàng )新點(diǎn)�。

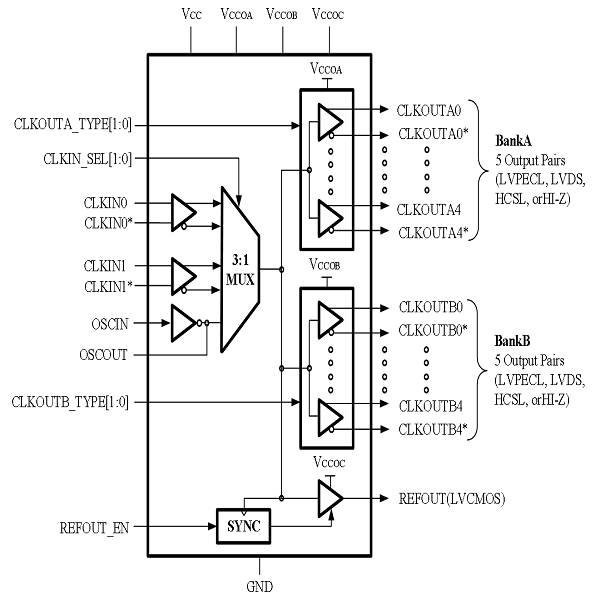

從5G到6G����,通信基站從僅支持通信信號的發(fā)送和接受升級至同時(shí)支持通信和感知�����,這便要求應用于通信系統的片上系統SOC擁有多種不同頻率����、不同性能的時(shí)鐘信號���,以支持復雜的信號處理�����、高速數據處理�����、高質(zhì)量通信和智能感知管理需求���。同時(shí)��,還需最大限度地降低時(shí)鐘抖動(dòng)可能對誤碼率�����、通信鏈路的穩定可靠性等產(chǎn)生的影響�。

傳統的SOC模擬鎖相環(huán)面積大且僅有一路輸出信號����,盡管數字型小數鎖相環(huán)可以克服面積�����、功耗等問(wèn)題�����,但是時(shí)間數字轉換器Time-to-Digital Converter(TDC)���、分數分頻器量化噪聲�、數字控制振蕩器Digital Controlled Oscillator(DCO)的相位噪聲之間的折中無(wú)法避免��,且極大地影響著(zhù)輸出的時(shí)鐘抖動(dòng)����。

因此如何在SOC上提供多個(gè)鎖相環(huán)時(shí)鐘信號�����,同時(shí)降低面積����、功耗和時(shí)鐘抖動(dòng)成業(yè)界關(guān)切的重點(diǎn)��?���;诖?���,賽思設計了一種開(kāi)環(huán)結構的小數分頻鎖相環(huán)量化噪聲校準技術(shù)��,并研制了可應用于6G通信技術(shù)的高性能SOC時(shí)鐘芯片���。

一種開(kāi)環(huán)結構的小數分頻鎖相環(huán)量化噪聲校準技術(shù)

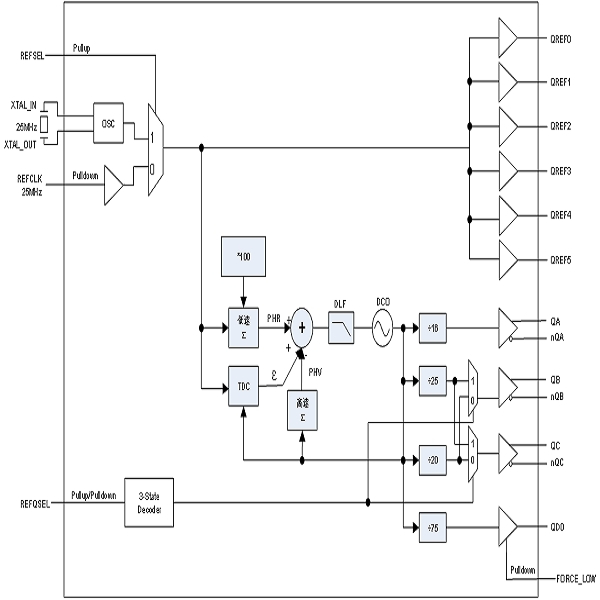

一種開(kāi)環(huán)結構的小數分頻鎖相環(huán)量化噪聲校準技術(shù)是為了滿(mǎn)足5G/6G高速數據通信系統中�,片上系統SOC對時(shí)鐘信號的高要求而設計的����。

該設計的的四大亮點(diǎn):

1��、消除量化噪聲����,降低時(shí)鐘抖動(dòng)���。在互補DTC校準技術(shù)的基礎上���,提出了量化噪聲校準技術(shù)�����,消除量化噪聲���,同時(shí)可以進(jìn)一步提高FOD時(shí)鐘輸出的整體噪聲性能�;

2��、降低面積�����、功耗����。本技術(shù)減少了DTC在數字控制字為0時(shí)候的補償電路�����,減少了DTC數量�,進(jìn)而降低功耗和面積��;

3�����、避免了頻率雜散抽取���、鎖相環(huán)濾波等校準技術(shù)帶來(lái)的電路復雜度����;

4����、全后臺校準��,相對原來(lái)的前臺校準+后臺校準���,提出的全后臺校準技術(shù)對工藝電壓溫度Process Voltage Temperature(PVT)變化不敏感�。

技術(shù)詳解:

為了提升系統相位噪聲性能���,在壓低帶外噪聲的情況下���,本技術(shù)提出采用小帶寬的設計�����,壓縮帶內噪聲對系統的貢獻��,例如圖1中帶寬從w3-->w1�����。在振蕩器為主的帶外噪聲一定且比較高的情況下����,為了提升相位噪聲性能�����,應該在壓低帶內噪聲的情況下�,采用寬帶寬的設計����,降低帶外噪聲對系統相位噪聲的貢獻���,例如圖1中帶寬從w2-->w4����。

時(shí)鐘系統

時(shí)鐘系統

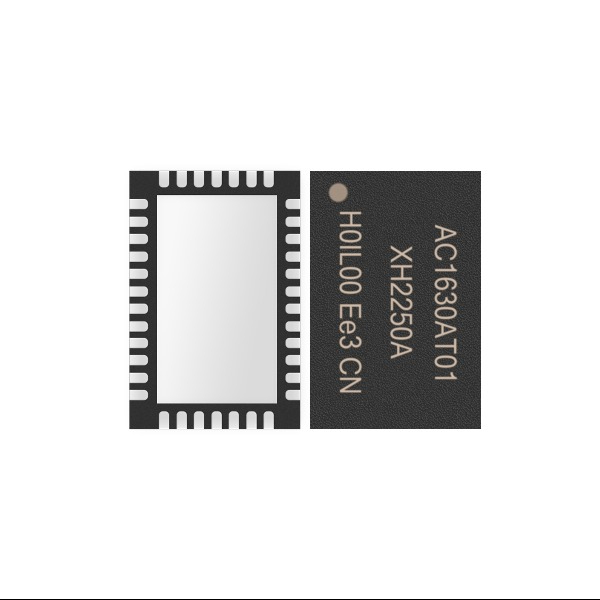

芯片

芯片

晶振&原子鐘

晶振&原子鐘

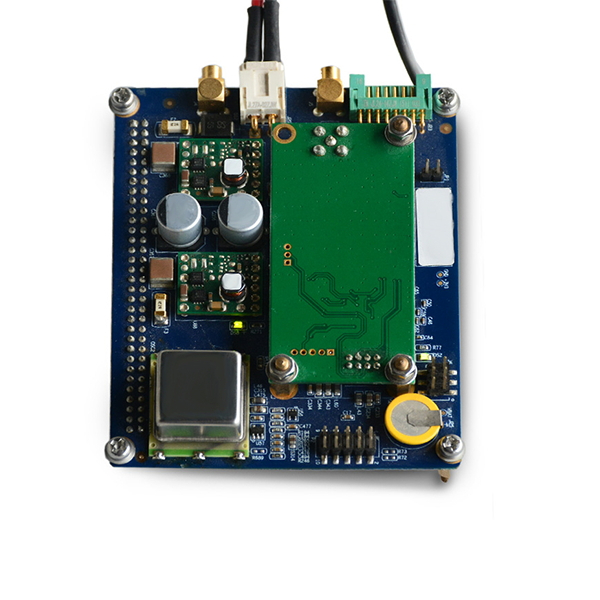

授時(shí)板卡

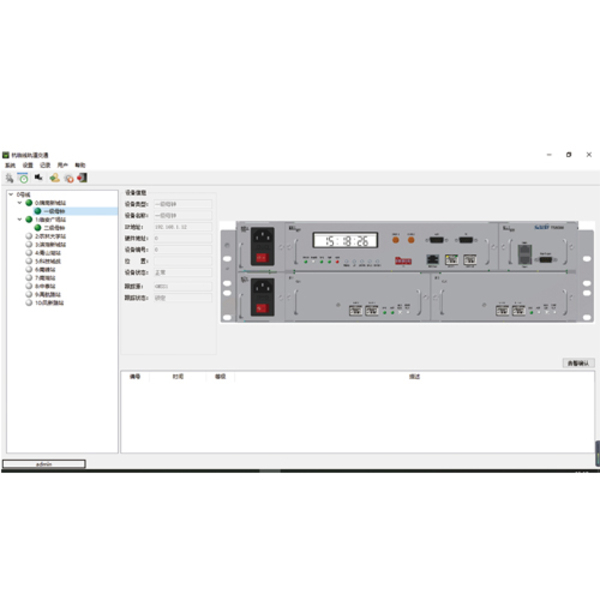

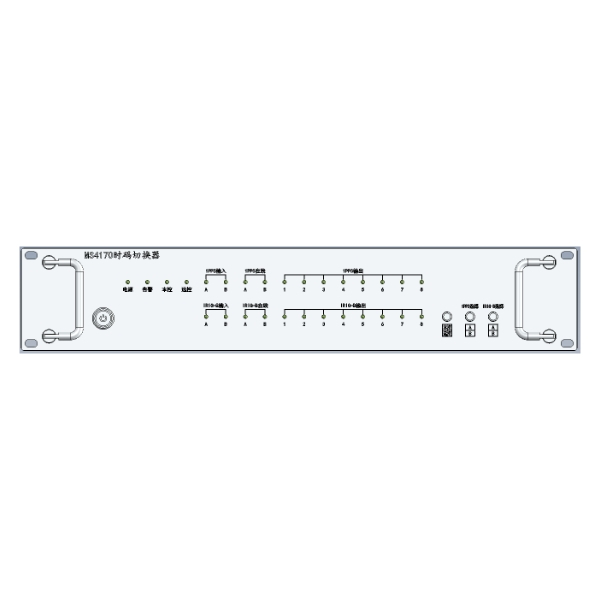

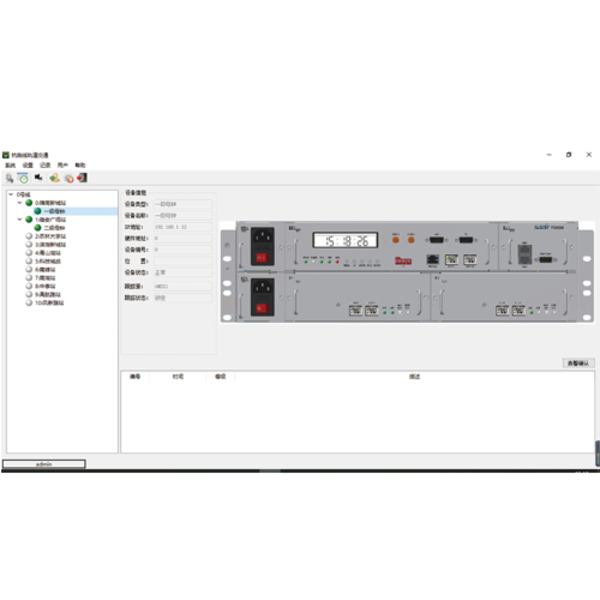

NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護裝置網(wǎng)同步設備/時(shí)頻一體化設備子母鐘系統BBU池時(shí)間同步時(shí)統設備鐘組設備測試儀器光纖雙向設備網(wǎng)管系統語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片晶振原子鐘授時(shí)模塊

授時(shí)板卡

NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護裝置網(wǎng)同步設備/時(shí)頻一體化設備子母鐘系統BBU池時(shí)間同步時(shí)統設備鐘組設備測試儀器光纖雙向設備網(wǎng)管系統語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片晶振原子鐘授時(shí)模塊

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò )

通信網(wǎng)絡(luò )

智慧交通

智慧交通

智能樓宇

智能樓宇

數據中心

數據中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思